## CONTROLLER PROGRAM SYNTHESIS FOR INDUSTRIAL MACHINES

by

Hans-Jörg Peter

A diploma thesis in the DEPARTMENT 6.2 - COMPUTER SCIENCE

Advisors

Prof. Bernd Finkbeiner, PhD Prof. Dr.-Ing. habil. Hartmut Janocha

SAARLAND UNIVERSITY, GERMANY

November 2005

## Erklärung

Hiermit versichere ich an Eides statt, dass ich die vorliegende Arbeit selbständig und unter ausschließlicher Verwendung der angegebenen Hilfsmittel angefertigt habe.

Saarbrücken, im November 2005

This work is dedicated to my grandparents Hannelore and Nikolaus Peter

### Abstract

In this thesis, a new synthesis algorithm for industrial controller programs is presented.

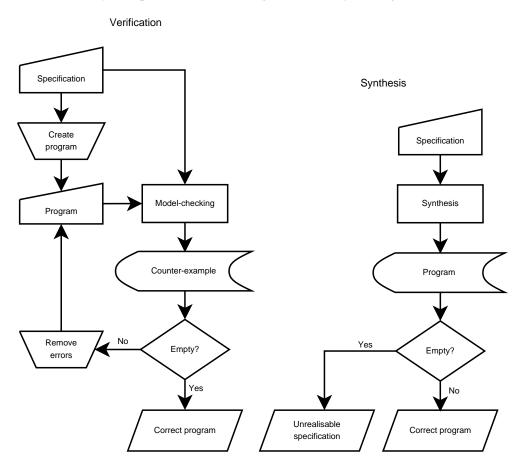

Verification and synthesis are the two basic approaches to guarantee that a system is correct. While verification requires the programmer to provide both the specification and the implementation, synthesis automatically transforms the specification into an implementation that is correct by construction.

The presented approach includes a new specification language that is geared towards usability in an industrial set-up. Specifications consist of two parts: a generic description of the machine components that is reused for different programs, and a description of the production goals that is specific to each program. The behaviour of the machine components is described by timed automata, while the production goals are captured by safety and bounded liveness properties.

The advantage of this approach is that the description of the goals, and thus of the behaviour of the overall system, is decoupled from the technical details of the machine components. This results in a high degree of re-usability, adaptivity, and maintainability. The specification of the machine components can be reused for different programs, and a reconfiguration of the machine no longer requires a time-consuming re-implementation.

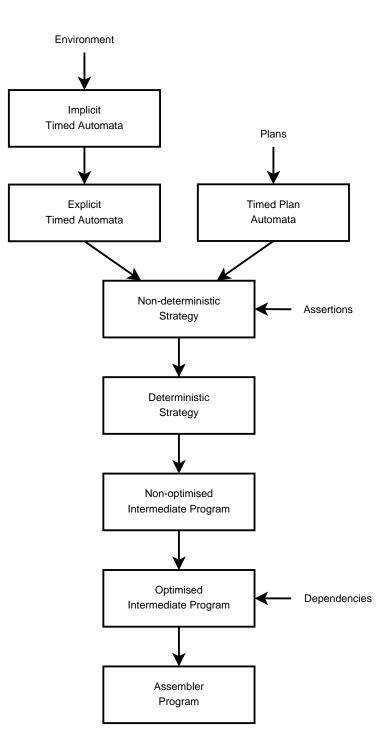

The synthesis problem is solved by finding a memory-less strategy in a safety game. A winning strategy is transformed into an intermediate controller program, which controls the machine such that the production aims are met. The intermediate program is improved in several optimisation steps before it is cross-compiled for a machine controller.

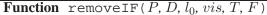

The approach is illustrated with a prototype implementation that includes a crosscompiler for IEC 1131-3 assembler code. The implementation has been applied in several case studies using the Siemens S7-300 programmable logic controller, which is the current industrial standard.

### Acknowledgements

First of all, thanks a lot to Prof. Bernd Finkbeiner, Joachim Fox, and Sven Schewe for giving me suggestions and valuable hints. In particular the discussions with Sven about safe and unsafe programs, as well as with Joachim about whether solving a problem by straight programming is easier than giving a formal specification, revealed some major issues that found their way into the thesis. Thanks to Prof. Hartmut Janocha for supporting me with technical equipment that made a real world application of the developed synthesis tool possible.

Furthermore, thanks to Martin Bauer for the helpful discussions and especially Lea Pfeifer for her patience and support, as well as to my parents Gertrud and Michael Peter.

# Contents

| 1 | Intr | oduction                                  | n                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 1                          |  |  |  |  |  |  |  |

|---|------|-------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------|--|--|--|--|--|--|--|

|   | 1.1  | Motiva                                    | ation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 1                          |  |  |  |  |  |  |  |

|   | 1.2  | Correc                                    | et Programs                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 2                          |  |  |  |  |  |  |  |

|   | 1.3  | Overvi                                    | iew                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 4                          |  |  |  |  |  |  |  |

|   | 1.4  | Related                                   | d Work                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 7                          |  |  |  |  |  |  |  |

| 2 | Prel | eliminaries                               |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |                            |  |  |  |  |  |  |  |

|   | 2.1  | Infinite                                  | e Games                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 9                          |  |  |  |  |  |  |  |

|   |      | 2.1.1                                     | Game Arena                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 9                          |  |  |  |  |  |  |  |

|   |      | 2.1.2                                     | Safety Games                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 10                         |  |  |  |  |  |  |  |

|   |      | 2.1.3                                     | Solving a Safety Game                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 10                         |  |  |  |  |  |  |  |

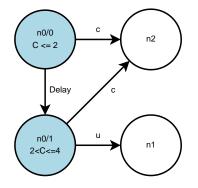

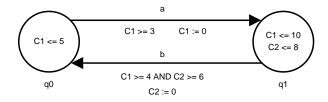

|   | 2.2  | Timed                                     | Automata                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 11                         |  |  |  |  |  |  |  |

|   |      | 2.2.1                                     | Infinite State Transition Graph                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 13                         |  |  |  |  |  |  |  |

|   |      | 2.2.2                                     | Clock Zones                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 14                         |  |  |  |  |  |  |  |

|   |      | 2.2.3                                     | Difference Bound Matrices                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 17                         |  |  |  |  |  |  |  |

|   |      | 2.2.4                                     | Complexity Considerations                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 19                         |  |  |  |  |  |  |  |

| 3 | Con  | nputatio                                  | onal Models                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 20                         |  |  |  |  |  |  |  |

|   | 3.1  | -                                         | Game Automata                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 20                         |  |  |  |  |  |  |  |

|   | 3.2  | Plan A                                    | utomata                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 21                         |  |  |  |  |  |  |  |

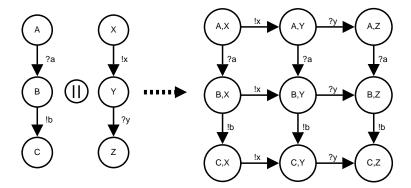

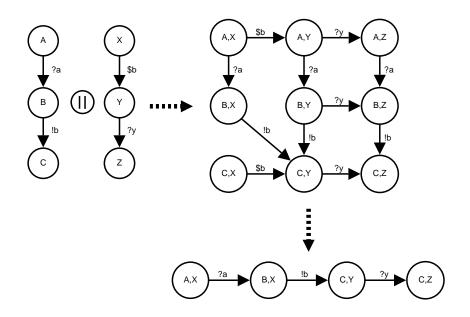

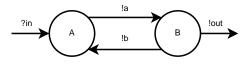

|   | 3.3  | Paralle                                   | Parallel Composition                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                            |  |  |  |  |  |  |  |

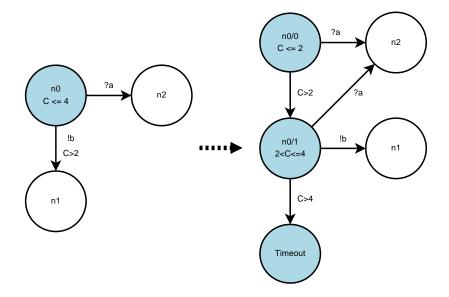

|   | 3.4  |                                           | bined State Space                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |                            |  |  |  |  |  |  |  |

| 4 | Spec | rificatio                                 | n Language                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 25                         |  |  |  |  |  |  |  |

| • | 4.1  | meano                                     | n Dunguage                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |                            |  |  |  |  |  |  |  |

|   |      | Plant <b>F</b>                            | Definition                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 25                         |  |  |  |  |  |  |  |

|   |      |                                           | Definition                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 25<br>26                   |  |  |  |  |  |  |  |

|   |      | 4.1.1                                     | Automaton Component                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 26                         |  |  |  |  |  |  |  |

|   |      | 4.1.1<br>4.1.2                            | Automaton ComponentHardware Component                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 26<br>27                   |  |  |  |  |  |  |  |

|   |      | 4.1.1<br>4.1.2<br>4.1.3                   | Automaton Component                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 26<br>27<br>28             |  |  |  |  |  |  |  |

|   |      | 4.1.1<br>4.1.2<br>4.1.3<br>4.1.4          | Automaton Component       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       . | 26<br>27<br>28<br>29       |  |  |  |  |  |  |  |

|   | 4.2  | 4.1.1<br>4.1.2<br>4.1.3<br>4.1.4<br>4.1.5 | Automaton Component                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 26<br>27<br>28<br>29<br>30 |  |  |  |  |  |  |  |

|   |      | 4.1.1<br>4.1.2<br>4.1.3<br>4.1.4<br>4.1.5 | Automaton Component       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       . | 26<br>27<br>28<br>29       |  |  |  |  |  |  |  |

|   | 4.3        | Semantics                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

|---|------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|   |            | 4.3.1 Automaton Component                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

|   |            | 4.3.2 Hardware Component                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

|   |            | 4.3.3 Operator Component                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

|   |            | 4.3.4 Assertions                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

|   |            | 4.3.5 Dependencies                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

|   |            | 4.3.6 State Guards                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

|   |            | 4.3.7 Plans                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| _ | ~          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| 5 |            | e Solving 40                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

|   | 5.1        | Zenoness                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

|   | 5.2        | Precomputation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

|   |            | 5.2.1 Clock Usage Analysis                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

|   |            | 5.2.2 Unique Choice Intervals                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

|   | 5.3        | Winning Controller State Space                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

|   |            | 5.3.1 Basic Functions and Operators                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

|   |            | 5.3.2 Forward Exploration                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

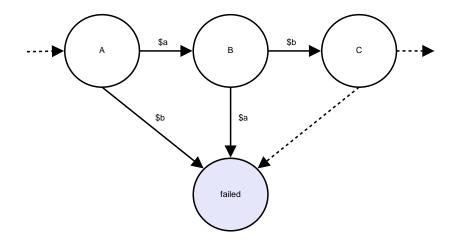

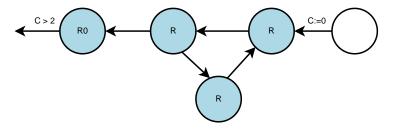

|   |            | 5.3.3 Reverse Fail State Removal 50                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

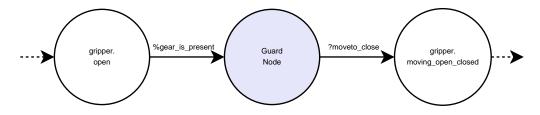

|   |            | 5.3.4 Special "Guarded State" Transition Type                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| 6 | Cod        | e Generation 54                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

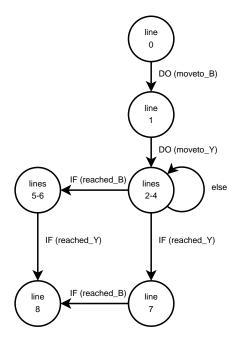

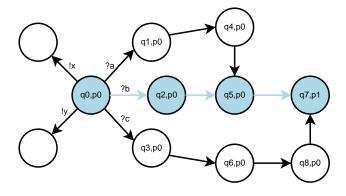

| U | 6.1        |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

|   | 6.2        | Intermediate Controller Language54Basic Functions and Operators57                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

|   | 6.3        | From Strategies to Controller Programs                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

|   | 0.3<br>6.4 | Selection of Controllable Transitions                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

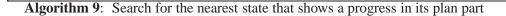

|   | 0.4<br>6.5 | Intermediate Code Generation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

|   | 0.5<br>6.6 |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

|   | 0.0        | 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

|   |            | 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

|   |            | 8                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

|   |            | 6.6.3Reference-inlining656.6.4Unreachable command-block removal66                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

|   |            | 6.6.5       Redundant GOTO removal       66                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

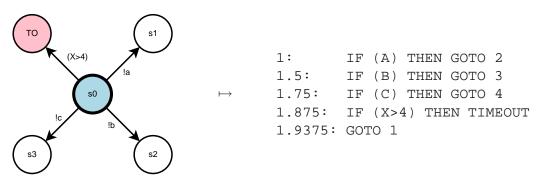

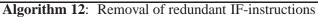

|   |            | 6.6.6         Redundant IF removal         66         66         66         66         66         66         66         66         66         66         66         66         66         66         66         66         66         66         66         66         66         66         66         66         66         66         66         66         66         66         66         66         66         66         66         66         66         66         66         66         66         66         66         66         66         66         66         66         66         66         66         66         66         66         66         66         66         66         66         66         66         66         66         66         66         66         66         66         66         66         66         66         66         66         66         66         66         66         66         66         66         66         66         66         66         66         66         66         66         66         66         66         66         66         66         66         66         66         66 |

|   | 6.7        | Assembler Cade Conservation 70                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

|   | 0.7        |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

|   |            | 6.7.1         Target System         70           6.7.2         IEC 1131-3 Code Compilation         70                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

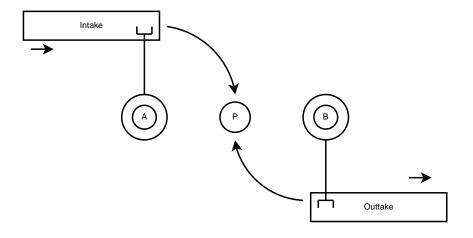

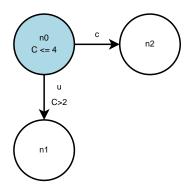

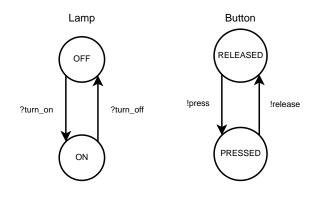

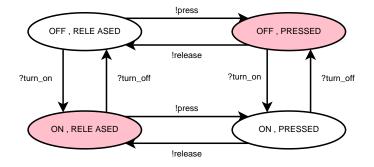

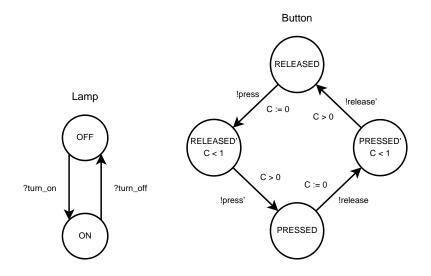

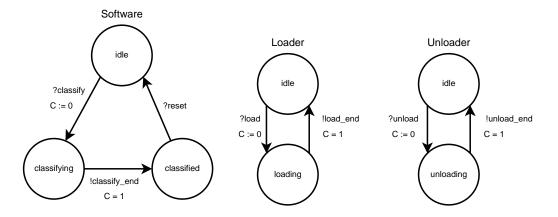

|   |            | 0.7.2 IEC 1151-5 Code Compilation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |